Schritt 3: Einzelne Module des FPGA

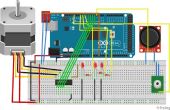

DFF: Dieses Projekt verwendet 2 8-Bit D-Flip Flops, verwendet, um die gewünschte Temperatur und die Toleranz zu speichern. Dies ermöglicht dem Benutzer, ihre Schalter, um eine neue Einstellung zu konfigurieren, ohne sporadische Verhalten des Lüfters. Die DFF hat 3 Eingänge: Clk (Uhr), d (7 Downto 0) (Eingabewert), En (Enable); und 1 Ausgang: f (7 Downto 0) (Ausgabewert). Auf die steigende Flanke der Uhr wenn der Enable-Eingang hoch ist dann der DFF legt den Ausgabewert fest, der aktuellen Eingabewert.

RCA: Dieses Projekt verwendet 2 8-Bit Ripple Carry Kreuzottern, verwendet, um die Eingabe Temperaturen anpassen um den Betrag der vom Benutzer angegebenen Toleranz. RCA hat 2 Eingänge: ein (7 Downto 0), B (7 Downto 0); und 1 Ausgang: S(7 downto 0) (Summe). RCA verwendet 7 voll Ottern und 1 addiert halbe Adder, fügen Sie die zwei Eingabewerte durch den Vergleich ihrer gleichen Größenordnung Bits, wodurch eine Summe, die die eingegebenen Zahlen darstellt.

Komparator: Dieses Projekt verwendet 3 8-Bit-Komparatoren, verwendet, um den aktuellen Zustand der Temperaturausgleich zu erkennen. Der Komparator hat 2 Eingänge: ein (7 Downto 0), B (7 Downto 0); und 2 Ausgänge: LT (weniger als), GT (größer als). Der Komparator Ausgang wird eine hohe, LT, stimmt AB.

Multiplexer: Dieses Projekt verwendet ein 8-Bit Multiplexer, um auszuwählen, was angezeigt werden soll, auf der sieben-Segment-Anzeige, mit 1-heiß codiert select Signal. Der Multiplexer hat 4 Eingänge: ein (7 Downto 0), B (7 Downto 0), C (7 Downto 0), D (7 Downto 0); 1 Wählen Sie Signal: Sel (4 Downto 0); und 1 Ausgang: heraus (7 Downto 0). Der multiplexer Ausgänge: D wenn das 4. Bit auswählen ist hoch, C Wenn der 3. Bit auswählen ist hoch, B wenn das 2. Bit auswählen ist hoch, A Wenn das 1. Bit auswählen ist hoch, und x "00" den Rest der Zeit.

Sseg_dec: Dieses Projekt verwendet eine sieben-Segment-Decoder zum Anzeigen von Informationen für den Benutzer über die aktuelle Temperaturwerte und Einstellungen aus den gespeicherten binären Werten in leicht lesbare Decimal. Die Sseg_dec hat 4 Eingänge: ALU_VAL(7 downto 0) (Eingang Binärzahl), Zeichen (signiert), gültig, CLK (Uhr); und 2 Ausgänge: DISP_EN(3 downto 0) (Ziffer Anoden), SEGMENTS(7 downto 0). Dieses Modul wurde von unserem Lehrer in einem Labor zur Verfügung gestellt und wurde von Bryan Mealy gemacht. In unserem Projekt haben wir nur unsignierte gültige Zahlen, so Zeichen '0' und gültig auf "1" festgelegt wurde. Normalerweise die eingegebenen Binärzahl in binär codierten Dezimalzahl umgewandelt wird, und dann die richtigen Segmente und Ziffer Anoden sind ausgeschaltet, aber für dieses Projekt, das wir die Anzeige änderten, um vollständig ausgeschaltet werden wenn die eingegebenen Binärzahl 0 war, um Energie zu sparen sollte nichts angezeigt werden muss.

Wenn Sie keine Änderungen an dem Programm vornehmen möchten, ist der Quellcode unten aufgeführt.